在GHz级的高速电路中,每一根走线都是潜在的“天线”,每一个过孔都可能成为信号的“陷阱”。

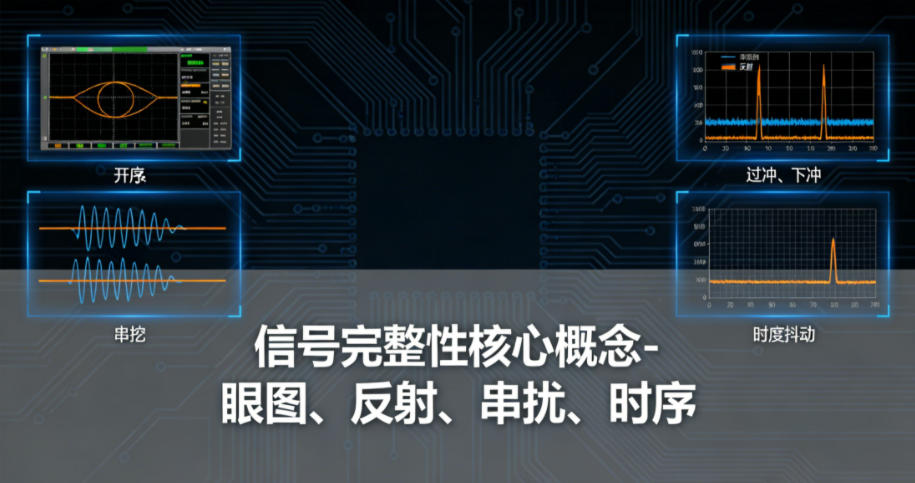

信号完整性(SI) 正是解决这些问题的关键学科。

今天,我们带你深入理解信号完整性的核心概念,并揭秘华垓技术如何在产品中运用SI技术实现卓越性能!

信号完整性是指信号在传输路径上保持其原始波形特征的能力,即在接收端能够准确还原发送端发出的逻辑电平。简单来说,就是确保“1”是“1”,“0”是“0”,不因传输效应而产生误判。

随着数字电路速率不断提升(DDR5、PCIe 5.0/6.0、SerDes 56Gbps),信号完整性问题已成为硬件研发成败的关键。

反射、串扰、地弹、时序抖动、损耗……

任何一个问题都可能导致系统不稳定甚至完全失效。

阻抗不连续导致信号反弹。

对策:控制特征阻抗(如50Ω单端、100Ω差分),匹配终端,优化过孔和分支。

相邻信号线间的电磁耦合。

对策:增大线间距(3W原则),引入防护地线,采用带状线结构。

时钟边沿位置的不确定性。

对策:低抖动时钟源,电源去耦,控制同步开关噪声。

高频下介质吸收和趋肤效应导致信号衰减。

对策:选用低损耗板材(如MEGTRON6),预加重/均衡技术。

全链路超低噪声架构,屏蔽驱动与保护环技术,将外部干扰降至5 fA/√Hz以下。

9路MIPI信号同步采集,严格等长布线,保证时钟同源,避免数据错位。

6000V隔离耐压设计,通过浪涌、脉冲群等EMC测试,确保恶劣环境下信号可靠。

我们拥有经验丰富的SI专家团队和先进的仿真平台,可为客户提供从PCB设计到系统级优化的完整服务。

获取更多硬核产品资讯与技术解决方案

© 2026 华垓技术 · 原创内容 · 转载请联系

专注嵌入式视觉解决方案,为智能硬件赋能

Copyright © 2021 北京一造电子技术有限公司 版权所有 备案号:京ICP备15066359号-1

技术支持:高搜互联

扫一扫咨询微信客服

扫一扫咨询微信客服